# TECHNICAL REPORT

### IEC TR 60068-3-12

First edition 2007-03

**Environmental testing –**

Part 3-12:

Supporting documentation and guidance – Method to evaluate a possible lead-free solder

reflow temperature profile

#### **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

#### Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

#### Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- IEC Web Site (www.iec.ch)

- Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/searchpub) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

IEC Just Published

This summary of recently issued publications (<a href="www.iec.ch/online\_news/">www.iec.ch/online\_news/</a> justpub) is also available by email. Please contact the Customer Service Centre (see below) for further information.

Customer Service Centre

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: chetsexv@iec.ch Tel: 141 22 919 02 11 Fax: 141 22 919 03 00

### **TECHNICAL REPORT**

### **IEC** TR 60068-3-12

First edition 2007-03

**Environmental testing** ·

Part 3-12:

Supporting documentation and guidance -Method to evaluate a possible lead-free solder

reflow temperature profile

© IEC 2007 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

P

### CONTENTS

| FOI      | REWC             | )RD                                                                                                                          | 4  |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------|----|

| 1        | Scop             | e                                                                                                                            | 6  |

| 2        | Basic            | S                                                                                                                            | 6  |

| 3        | Boar             | ds under investigation                                                                                                       | 7  |

|          | 3.1              | Test board approach                                                                                                          |    |

|          | 3.2              | Production board approach                                                                                                    |    |

| 4        | Temp             | perature tolerances                                                                                                          | 8  |

|          | 4.1              | Temperature tolerances in Study A                                                                                            | 8  |

| 5        | 4.2<br>Peak      | Temperature tolerance and board size influence in Study B                                                                    |    |

|          | 5.1              | Peak form and width in Study A                                                                                               | 10 |

|          | 5.2              | Reflow oven investigation in Study B                                                                                         |    |

| 6        |                  | sification                                                                                                                   |    |

|          | 6.1              | Device classification in Study A                                                                                             | 11 |

|          | 6.2              | Device classification in Study A                                                                                             | 12 |

| 7        |                  |                                                                                                                              |    |

|          | 7.1              | Determined lead-free reflow temperature profile in Study A                                                                   |    |

| •        | 7.2              | Lead-free reflow temperature profile approach in Study B                                                                     |    |

| 8<br>Bib |                  | ohy                                                                                                                          |    |

|          | ole 1 –<br>rance | Measured temperatures of devices and values including lower and upper                                                        | 12 |

|          |                  | Possible temperature classification of nonhermetic solid state surface mount eferting to volume and thickness of the devices |    |

|          |                  | Proposed requirements for a lead-free device qualification reflow are profile in numbers                                     | 14 |

|          |                  | 70/5/w.                                                                                                                      |    |

| 233      | °C               |                                                                                                                              | 7  |

|          |                  | <ul> <li>Position of the assembled devices and temperature dependence on the sition</li> </ul>                               | 8  |

| Fig      | ure 3            | - Lower and upper temperature tolerances of the reflow solder profile                                                        | 9  |

| Fig      | ure 4            | - Temperature tolerance and board size influence                                                                             | 9  |

| _        |                  | - Hat type peak profile with 40 s at $T_{\text{max}}$ - 5 K = 255 °C for the small devices $^{\circ}$ CB                     | 10 |

| Fig      | ure 6            | – $\Delta T$ by different reflow oven capabilities                                                                           | 11 |

| Fig      | ure 7            | - Representative test board measurements                                                                                     | 11 |

| Fig      | ure 8            | - Example of the small board (camcorder)                                                                                     | 13 |

| Fig      | ure 9            | - Example of the mid-size board (PC)                                                                                         | 13 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### **ENVIRONMENTAL TESTING -**

### Part 3-12: Supporting documentation and guidance – Method to evaluate a possible lead-free solder reflow temperature profile

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to EC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the vormative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC 60068-3-12, which is a technical report, has been prepared by IEC technical committee 91: Electronics assembly technology.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 91/601A/DTR   | 91/636A/RVC      |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

A list of all the parts in the IEC 60068 series, under the general title *Environmental testing*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- · withdrawn,

- · replaced by a revised edition, or

- amended.

#### **ENVIRONMENTAL TESTING -**

## Part 3-12: Supporting documentation and guidance – Method to evaluate a possible lead-free solder reflow temperature profile

#### 1 Scope

This part of IEC 60068 serves as a Technical Report and presents two approaches for establishing a possible temperature profile for a lead-free reflow soldering process using SnAgCu solder paste.

This process covers a great variety of electronic products, including a large range of package sizes (molded active electronic components, passive components and electromechanical components).

Study A addresses requirements needed in the production of automotive electronic control units (ECU). These requirements include, but are not limited to, measurement and production tolerances.

Study B represents consumer electronics products and includes reflow oven capability, board design and package sizes.

#### 2 Basics

The process temperature for SnPb solder paste has a wide margin due to the liquid temperature of the solder alloy. During reflow soldering, temperature differences between components exist but are not critical. The process temperature of SnAgCu solder paste is about 20 K to 30 K higher than SnPb solder paste. Furthermore the temperature difference between components (AT) becomes wider and sometimes heat resistance temperature of components is exceeded.

To avoid soldering failures which could be very harmful in safety related applications and also generate higher failure costs, the capability of the soldering process is very important. A compromise between the temperature requirements of highly reliable solder joints and the limited solder hear resistance of the electronic devices has to be found. In addition, the different aspects of mass production have to be covered. To achieve a reliable solder joint, the conventional reflow soldering process with eutectic SnPb solder paste is usually performed at a minimum peak temperature of about 203 °C at the coldest solder joint (i.e. at least 20 K above the liquid temperature of SnPb  $T_{\text{liquid}} = 183$  °C).

The selected lead-free solder is SnAgCu with a melting point at around  $T_{\text{liquid}}$  = 217 °C [1] <sup>1</sup>. It is a generally preferred material for lead-free reflow and wave soldering in mass production [2]. Using SnAgCu solder paste, it is not possible to solder the coldest solder joints at least 20 K above the liquid temperature ( $T_{\text{liquid}}$  = 217 °C), which would result in minimum temperatures of 237 °C. When the coldest solder joint is 237 °C, the temperature spread between small and large devices, small semiconductor, and passive components, as well as the printed circuit board (PCB), will be so large that the devices will not survive the heat impact. Despite the aim to achieve a relatively low temperature at the coldest solder joint, the reliability of the solder joint has to be assured (for instance, for safety related applications in automotive industry).

<sup>1</sup> References in square brackets refer to the bibliography.

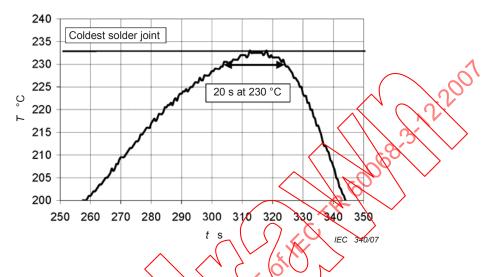

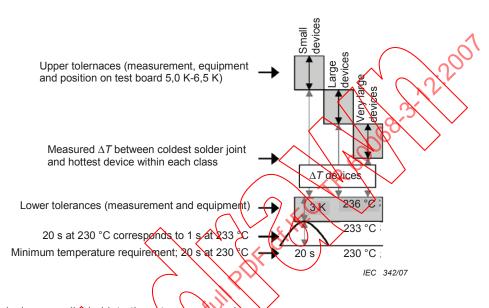

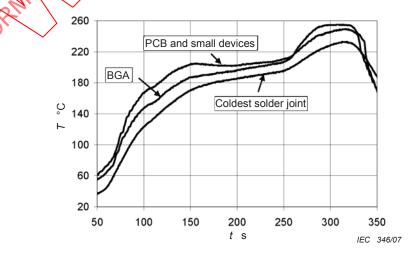

To reach this target in Study A, the temperature at the coldest solder joint is taken to be  $T_{\rm min}$  = 230 °C, minimum for 20 s, which is just 13 K above the melting temperature. This corresponds to 1 s at 233 °C resulting from the peak shape (see Figure 1). From a physical point of view, the risk of insufficient solder wetting during mass production is significantly higher if the solder joint temperature is lower as the above mentioned 230 °C. In addition, new lead-free termination finishes (like tin layers with a post bake process or very thin NiPdAu finishes) are known to wet poorer than conventional SnPb pin finishes.

Figure 1 – Curve shape for a peak temperature of at least 20 s at 230 °C and 1 s at 233 °C

The experiments had been performed under mass production conditions (850 mm/min) on the newest oven equipment, i.e. multiple heating zones, full convection,  $N_2$  atmosphere. Seven ovens from European and American manufacturers were evaluated in 2003. Only four of the seven ovens were able to fulfill the given requirements concerning the temperature spread. These were the ovens which were used in the study A.

If the components use selected material regardless of the cost, it may solve the heat resistance issue but it might not be feasible for industries. To overcome this problem, two approaches are used to come to a compromise with reasonable cost. One is from components by improving heat resistance and the other one from assembly including board design (alignment of components, board size, etc.) and reflow oven capability (heating method, number of heating zone, etc.) by reducing  $\Delta T$ .

#### 3 Boards under investigation

#### 3.1 Test board approach

For the experiment in Study A, a special test PCB was designed. Polyimide resin with a glass transition temperature of  $T_{\rm g}$  = 260 °C was used as base material for the PCB. The test board can represent the whole automotive ECU spectrum. The largest temperature difference ( $\Delta T$ ) between the coldest solder joint and the hottest point existing on this printed circuit assembly (PCA) spectrum is reflected on this test board ( $\Delta T$  can be even larger for even more complex PCAs). The coldest solder joint was represented by a defined thermal mass. Its temperature behavior was correlated with the temperatures of the coldest solder joints on serial boards.

#### 3.2 Production board approach

For Study B, PCB and reflow oven are taken from actual production.

#### 4 Temperature tolerances

#### 4.1 Temperature tolerances in Study A

For tolerances during temperature profiling, different systematic failures shall be considered. First of all, there is the failure during temperature measurement itself. The measurement was performed in the centre on top of the packages with a well defined and repeatable preparation technique. Nevertheless, the failure due to preparation had to be fixed within  $\pm 1,0$  K. In addition, the thermocouple (NiCrNi), together with the evaluation unit has an accuracy of  $\pm 1,5$  K for pre-selected thermocouples. According to IEC 60584-2 the NiCrNi thermocouples, class K, tolerance class 1 are specified with a tolerance of  $\pm 1,5$  K for just the thermocouple itself without the measurement unit. Based on suppliers indication and own measurements, the furnace tolerance based on furnace load is  $\pm 0,5$  K and the furnace tolerance for long term stability is  $\pm 2,5$  K. The long term stability of the furnaces should be improved in the future.

| _ | Thermocouple with measurement unit: | ±1,5 K |                                        |

|---|-------------------------------------|--------|----------------------------------------|

| _ | Preparation:                        | ±1,0 K |                                        |

| _ | Furnace load:                       | ±0,5 K | V/ 1904 \                              |

| - | Long term stability of furnace:     | ±2,5 K | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

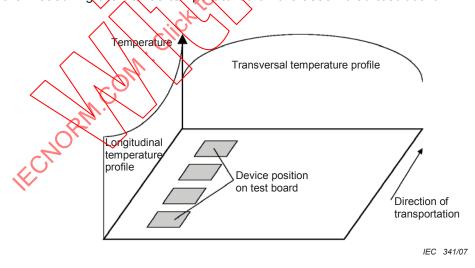

Because these errors are independent, the Gaussian error propagation can be applied, which results in a total tolerance of  $\pm 3.0$  K, due to measurement errors and variations in mass production. The tolerance of -3.0 K results in the requirement to profile the coldest solder joint at 236 °C, instead of 233 °C (i.e. 233 °C + 3.0 K). This tolerance is known as the "lower tolerance". In addition to the measurement errors and variations due to mass production, the influences of the test board have to be considered. The measured temperatures of the electronic components depend also on the position on the test board because of the longitudinal and transversal temperature spread in the furnace and along the test board (see Figure 2). These temperature differences are the result of the heat flow conditions in the furnace and around the test board. Therefore, the actual temperature of a device can be up to 3,5 K higher than the measured values at the position where the device is mounted on the test board. The temperature dependence on the device position was measured independently before measuring the device temperatures on the assembled test board.

Figure 2 – Position of the assembled devices and temperature dependence on the device position

The thermal mass on the test board, which represents the coldest solder joint on the serial boards, was designed in such a way that position-dependent tolerances were already included. The upper temperature tolerances consist of the position-dependent temperature tolerances of 2 K to 3,5 K and the above mentioned +3 K. This leads to a total upper tolerance of 5 K to 6,5 K. Regarding the whole temperature window of the lead-free soldering process, a total position dependent temperature tolerance of 8 K to 9,5 K has to be added to the measured  $\Delta T$  spread of the devices (see Figure 3).

NOTE Electronic devices are divided into three temperature classes.

Figure 3 – Lower and upper temperature to erances of the reflow solder profile

#### 4.2 Temperature tolerance and board size influence in Study B

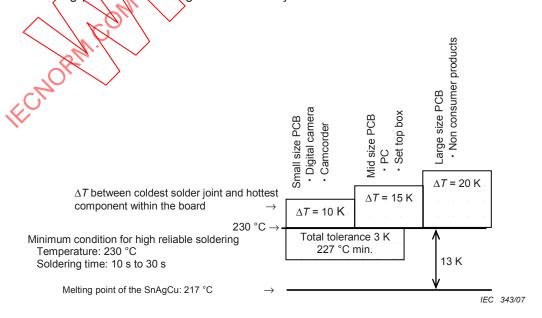

In the consumer board study, measured temperature includes lower temperature tolerance and upper temperature tolerance. Therefore at the coldest solder joint temperature of 230 °C, the 'worst-case' temperature becomes 227 °C (i.e. 230 °C - 3 K) which is still 10 K higher than the melting point of the ShAgCu solder alloy.

Figure 4 – Temperature tolerance and board size influence

#### 5 Peak form and width

#### 5.1 Peak form and width in Study A

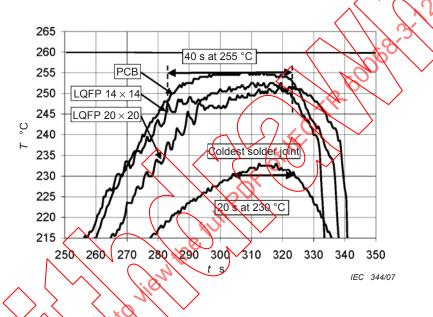

The requirements were to maintain a temperature of at least 230 °C for 20 s at the coldest solder joint, and to limit the peak package temperature of the smallest devices (e.g. SOT23, small LQFP, TopLEDs and passive components) to  $T_{\rm peak} \le 260$  °C. In order to meet these requirements, a soak type preheating, as well as a hat type soldering peak were necessary in the investigation. The soak type preheating allowed the temperatures of the individual packages to be close to each other upon entry into the peak zone (see Figure 7). The hat type form of the soldering peak was used to minimize the temperature differences between the individual packages during reflow soldering. After conducting the experiment, it was discovered that the hat type form of the soldering peak required a soak time of 40 s at  $t_{\rm max} - t_{\rm max} = 0.000$  °C for the hottest devices on the PCB (see Figure 5).

NOTE Temperature tolerances are included.

Figure 5 – Hat type peak profile with 40 s at  $T_{\text{max}}$  – 5 K = 255 °C for the small devices and the PCB

#### 5.2 Reflow over investigation in Study B

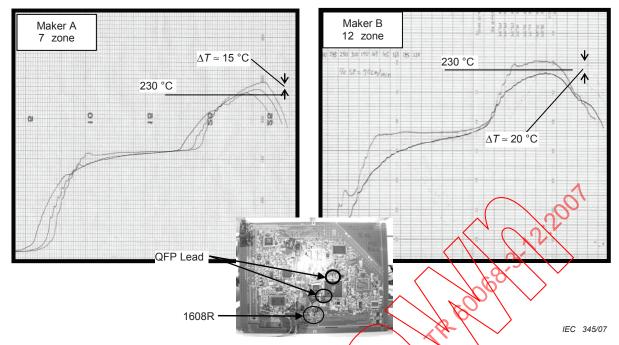

Figure 6 shows temperature profiles on QFP lead and 1608 size SMD resistor using the same board but different reflow ovens. Even reflow oven (Maker B) having more heating zones shows wider  $\Delta T$  than Maker A oven. Thus  $\Delta T$  does not depend on the number of heating zones of the reflow oven but on the design of the reflow oven.

The peak reflow temperature for smallest components may vary by reflow oven being used. Also board size and board design are other factors affecting the peak reflow temperature.

Figure 6 –  $\Delta T$  by different reflow oven capabilities

#### 6 Classification

#### 6.1 Device classification in Study A

To classify the non-hermetic solid state surface mount devices into temperature groups with respect to the reflow peak, the heat capacity and heat conductivity should be taken into consideration. To simplify the study, the component similarity with respect to the composition (molded silicon) is taken into account and only the package volume and thickness are considered. In Figure 7, some typical temperature measurements of molded components using the described test board with a soak preheating and a hat type reflow soldering peak are shown. The transportation speed was 850 mm/min and the temperature measurements were performed on top centre of the packages. In total, the temperature profiles for 19 characteristic molded package types and several passive and electromechanical devices were measured on a multiple heating zone reflow oven with full convection. Between the coldest solder joint and the PCB itself, temperature difference of 13 K was measured. Small plastic components like small connectors, switches or TopLEDs showed even higher peak package temperatures with a temperature difference of 17 K from the coldest solder joint [3,4].

NOTE Temperature tolerances are included.

Figure 7 - Representative test board measurements

Table 1 shows the measured temperatures and the temperatures achieved when the lower and upper tolerances are being added. Temperatures shown are for several characteristic molded devices with different peak temperatures.

Table 1 – Measured temperatures of devices and values including lower and upper tolerances

|                      | Temperature             |                          |                                    |                          |                                    |

|----------------------|-------------------------|--------------------------|------------------------------------|--------------------------|------------------------------------|

| Device               | Measured<br>value<br>°C | Lower<br>tolerance<br>°C | Including lower<br>tolerance<br>°C | Upper<br>tolerance<br>°C | Including upper<br>tolerance<br>°C |

| Coldest solder joint | 233,0                   | 3,0                      | 236,0                              |                          | 3                                  |

| PLCC52               | 234,0                   | 3,0                      | 237,0                              | 6.0                      | 243,0                              |

| TO263                | 239,5                   | 3,0                      | 242,5                              | 5,0                      | 247,5                              |

| BGA (24 mm x 24 mm)  | 240,5                   | 3,0                      | 243,5                              | 8,0                      | 249,5                              |

| LQFP (14 mm x 14 mm) | 243,5                   | 3,0                      | 256,5                              | 6,0                      | 252,5                              |

| PCD (SOT-devices)    | 247,0                   | 3,0                      | 250,0                              | 5.0                      | 255,0                              |

NOTE The upper tolerance is dependent on the position of the device on the PSB. The lower tolerance of 3,0 K represents the value that the minimum solder joint temperature has to be raised to due to the mentioned measurement and process tolerances.

In these examples, the maximum temperature difference between actual measured and tolerance corrected values was 9,5 k. These corrected temperatures represent the theoretically possible maximum package temperatures for the devices during reflow soldering. Referring to molded components (most active components) their internal structure is very similar. The specific heat capacity and the thermal conductivity do not deviate significantly (metal based lead frame/silicon/mold compound). Therefore, it is possible to create temperature classes for the solder heat resistance referring to volume and thickness of the molded devices. But, this is not possible for the wide range of passive and electromechanical components. Some of the non-molded components reached peak temperatures of 260 °C. In addition, many of the small molded components are commonly qualified with a 260 °C peak temperature reflow profile. Therefore, the upper temperature device group was defined as the 260 °C class. Furthermore, a class of 250 °C for large molded components and a class of 245 °C for very large molded components was set.

Table 2 Possible temperature classification of nonhermetic solid state surface mount devices referring to volume and thickness of the devices

| Thickness Volume                                                                 | < 350 mm <sup>3</sup> | 350 mm <sup>3</sup> – 2 000 mm <sup>3</sup> | > 2 000 mm <sup>3</sup> |  |  |

|----------------------------------------------------------------------------------|-----------------------|---------------------------------------------|-------------------------|--|--|

| < 1,6 mm                                                                         | 260 (- 0) °C          | 260 (- 0) °C                                | 260 (- 0) °C            |  |  |

| 1,6 mm - 2,5 mm                                                                  | 260 (- 0) °C          | 250 (- 0) °C                                | 250 (- 0) °C            |  |  |

| > 2,5 mm                                                                         | 260 (- 0) °C          | 250 (- 0) °C                                | 245 (- 0) °C            |  |  |

| NOTE The package volume excludes external terminals and non-integral heat sinks. |                       |                                             |                         |  |  |

#### 6.2 Board classification in Study B

Between coldest solder joint and hottest component package or PCB  $\Delta T$  ranks from 1 K for small boards to 9 K for mid-size boards.

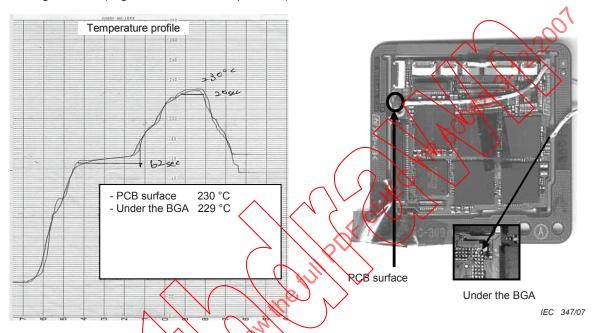

Figure 8 shows temperature profiles of the PCB surface and under the BGA on the small board. The maximum temperature under the BGA is 229  $^{\circ}$ C with 20 s above 225  $^{\circ}$ C and the maximum temperature of the PCB is 230  $^{\circ}$ C.

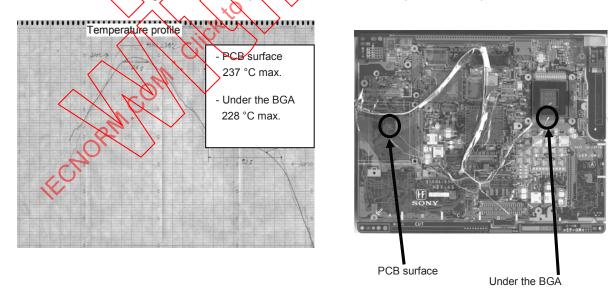

Figure 9 shows temperature profiles of the PCB surface and under the BGA on the mid-size board. The maximum temperature under the BGA is 228 °C with 26 s above 225 °C and the maximum temperature of the PCB is 237 °C.

From this study,  $\Delta T$  between coldest solder joint and hottest component package or PCB could be assumed as follows (refer to Figure 4);

Small size board (e.g., digital camera, camcorder): 10 K

Mid-size board (e.g., PC, set top box): 15 K

Large board (e.g., non-consumer product): 20 K

Figure 8 - Example of the small board (camcorder)

IEC 348/07

Figure 9 - Example of the mid-size board (PC)

#### 7 Consideration for a lead-free reflow temperature profile

#### 7.1 Determined lead-free reflow temperature profile in Study A

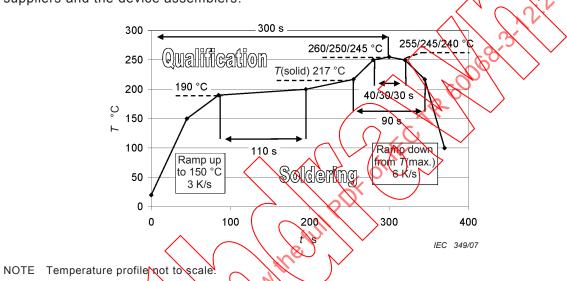

The performed measurements and the given argumentation lead to a possible reflow profile, which covers the described requirements of lead-free mass production (Figure 10). Once a device is qualified, using this reflow profile, it can be used in a wide range of electronic control units. To assess the components ability to withstand the solder process the devices should be subjected to soldering simulation at least three times using this temperature profile. This is necessary to ensure the reliability of the device during more than one reflow soldering process. Soldering in mass production shall be performed below this limiting temperature line to ensure that the device will not be stressed too much during the assembly process. Therefore, the proposed reflow profile could help define the borders between the device suppliers and the device assemblers.

Figure 10 – Lead-free reflow temperature profile for device qualification regarding to the solder heat resistance

In Table 3 the presented lead-free reflow profile is given in numbers.

Table 3 – Proposed requirements for a lead-free device qualification reflow temperature profile in numbers

| Profile features                                       | Small devices                                          | Large       | Very large  |  |

|--------------------------------------------------------|--------------------------------------------------------|-------------|-------------|--|

| Pre-heat                                               |                                                        |             |             |  |

| Ramp-up rate to 150 °C                                 | 3 K/s (average value over 10 s)                        |             |             |  |

| Time from 190 °C to 200 °C                             | Min. 110 s                                             |             |             |  |

| Peak                                                   |                                                        |             |             |  |

| Ramp-up rate from 200 °C to $T_{\rm peak}$             | 0,5 K/s - 3 K/s (average value over 10 s)              |             |             |  |

|                                                        |                                                        |             |             |  |

| Time above T <sub>solidus</sub> (min. 217 °C)          | Min. 90 s                                              |             |             |  |

| Peak temperature T <sub>peak</sub>                     | 260 (-0) °C                                            | 250 (-0) °C | 245 (-0) °C |  |

| Time above $T_{ m peak}$ – 5 H                         | Min. 40 s                                              | Min. 30 s   | Min. 30 s   |  |

| Cooling                                                |                                                        |             |             |  |

| Ramp-down rate from T <sub>solidus</sub> (min. 217 °C) | Up to 6 K/s (average value over 10 s) device dependent |             |             |  |

| General                                                |                                                        |             |             |  |

| Time 25 °C to T <sub>peak</sub>                        | Min. 300 s                                             |             |             |  |