**NORME

INTERNATIONALE

INTERNATIONAL

STANDARD**

**CEI

IEC

61188-1-2**

Première édition

First edition

1998-04

**Cartes imprimées et cartes imprimées équipées –

Conception et utilisation –**

**Partie 1-2:

Prescriptions génériques –

Impédance contrôlée**

**Printed boards and printed board assemblies –

Design and use –**

**Part 1-2:

Generic requirements –

Controlled impedance**

Numéro de référence

Reference number

CEI/IEC 61188-1-2:1998

## Numéros des publications

Depuis le 1er janvier 1997, les publications de la CEI sont numérotées à partir de 60000.

## Publications consolidées

Les versions consolidées de certaines publications de la CEI incorporant les amendements sont disponibles. Par exemple, les numéros d'édition 1.0, 1.1 et 1.2 indiquent respectivement la publication de base, la publication de base incorporant l'amendement 1, et la publication de base incorporant les amendements 1 et 2.

## Validité de la présente publication

Le contenu technique des publications de la CEI est constamment revu par la CEI afin qu'il reflète l'état actuel de la technique.

Des renseignements relatifs à la date de reconfirmation de la publication sont disponibles dans le Catalogue de la CEI.

Les renseignements relatifs à des questions à l'étude et des travaux en cours entrepris par le comité technique qui a établi cette publication, ainsi que la liste des publications établies, se trouvent dans les documents ci-dessous:

- «Site web» de la CEI\*

- Catalogue des publications de la CEI

Publié annuellement et mis à jour régulièrement

(Catalogue en ligne)\*

- Bulletin de la CEI

Disponible à la fois au «site web» de la CEI\* et

comme périodique imprimé

## Terminologie, symboles graphiques et littéraux

En ce qui concerne la terminologie générale, le lecteur se reportera à la CEI 60050: *Vocabulaire Electrotechnique International (IEV)*.

Pour les symboles graphiques, les symboles littéraux et les signes d'usage général approuvés par la CEI, le lecteur consultera la CEI 60027: *Symboles littéraux à utiliser en électrotechnique*, la CEI 60417: *Symboles graphiques utilisables sur le matériel. Index, relevé et compilation des feuilles individuelles*, et la CEI 60617: *Symboles graphiques pour schémas*.

\* Voir adresse «site web» sur la page de titre.

## Numbering

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series.

## Consolidated publications

Consolidated versions of some IEC publications including amendments are available. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

## Validity of this publication

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology.

Information relating to the date of the reconfirmation of the publication is available in the IEC catalogue.

Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is to be found at the following IEC sources:

- IEC web site\*

- Catalogue of IEC publications

Published yearly with regular updates

(On-line catalogue)\*

- IEC Bulletin

Available both at the IEC web site\* and as a printed periodical

## Terminology, graphical and letter symbols

For general terminology, readers are referred to IEC 60050: *International Electrotechnical Vocabulary* (IEV).

For graphical symbols, and letter symbols and signs approved by the IEC for general use, readers are referred to publications IEC 60027: *Letter symbols to be used in electrical technology*, IEC 60417: *Graphical symbols for use on equipment. Index, survey and compilation of the single sheets* and IEC 60617: *Graphical symbols for diagrams*.

\* See web site address on title page.

# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI

IEC

**61188-1-2**

Première édition

First edition

1998-04

**Cartes imprimées et cartes imprimées équipées –

Conception et utilisation –**

**Partie 1-2:

Prescriptions génériques –

Impédance contrôlée**

**Printed boards and printed boards assemblies –

Design and use –**

**Part 1-2:

Generic requirements –

Controlled impedance**

© IEC 1998 Droits de reproduction réservés — Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'éditeur.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission

Telefax: +41 22 919 0300

3, rue de Varembé Geneva, Switzerland

e-mail: [inmail@iec.ch](mailto:inmail@iec.ch)

IEC web site <http://www.iec.ch>

Commission Electrotechnique Internationale

International Electrotechnical Commission

Международная Электротехническая Комиссия

CODE PRIX

PRICE CODE

*Pour prix, voir catalogue en vigueur

For price, see current catalogue*

## SOMMAIRE

|                                                                                                 | Pages |

|-------------------------------------------------------------------------------------------------|-------|

| AVANT-PROPOS .....                                                                              | 4     |

| INTRODUCTION .....                                                                              | 6     |

| <br>Articles                                                                                    |       |

| 1 Domaine d'application .....                                                                   | 8     |

| 2 Références normatives .....                                                                   | 8     |

| 3 Vue d'ensemble de la conception technique .....                                               | 8     |

| 3.1 Sélection du dispositif .....                                                               | 8     |

| 3.2 Intraconnexion .....                                                                        | 10    |

| 3.3 Cartes imprimées et cartes imprimées équipées .....                                         | 12    |

| 3.4 Prescriptions de performance .....                                                          | 16    |

| 3.5 Répartition de la puissance .....                                                           | 36    |

| 4 Conception des circuits d'impédance contrôlée .....                                           | 38    |

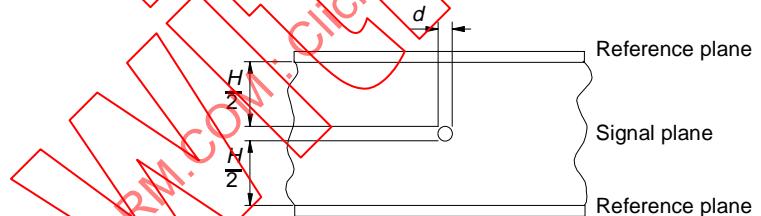

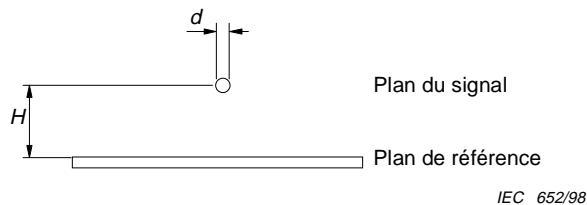

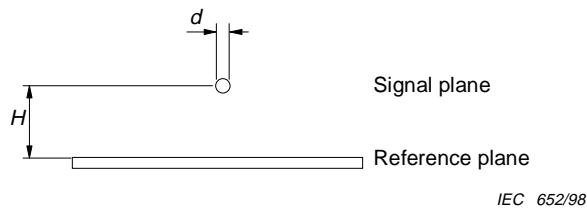

| 4.1 Configurations .....                                                                        | 38    |

| 4.2 Equations .....                                                                             | 40    |

| 4.3 Règles de conception d'impédance contrôlée .....                                            | 46    |

| 4.4 Règles de diaphonie .....                                                                   | 48    |

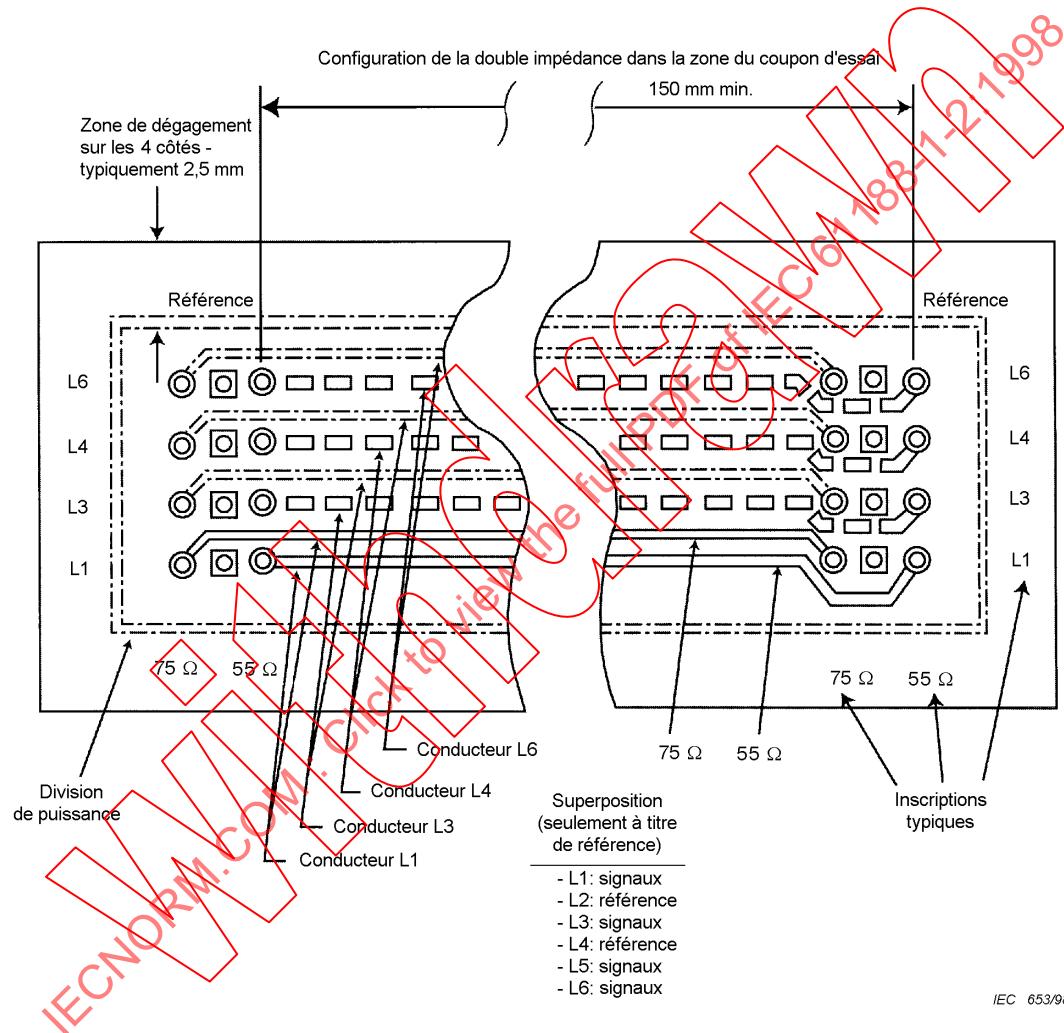

| 4.5 Règles de conception de coupon .....                                                        | 50    |

| 4.6 Règles relatives au découplage/condensateur .....                                           | 54    |

| 5 Conception relative à la fabrication .....                                                    | 58    |

| 5.1 Règles de processus en CAO (conception assistée par ordinateur) .....                       | 58    |

| 5.2 Complexité de la conception et corrélation avec le coût .....                               | 58    |

| 6 Description des données .....                                                                 | 58    |

| 6.1 Détails de construction .....                                                               | 60    |

| 6.2 Isolation des données par classe de filet (bruit, cadencement, capacité et impédance) ..... | 60    |

| 6.3 Performances électriques .....                                                              | 62    |

| 7 Matériaux .....                                                                               | 62    |

| 7.1 Systèmes résineux .....                                                                     | 62    |

| 7.2 Renforts .....                                                                              | 62    |

| 7.3 Feuilles préimprégnées, couches de liaison et adhésifs .....                                | 64    |

| 7.4 Dépendance vis-à-vis de la fréquence .....                                                  | 64    |

| 8 Fabrication .....                                                                             | 64    |

| 8.1 Généralités .....                                                                           | 64    |

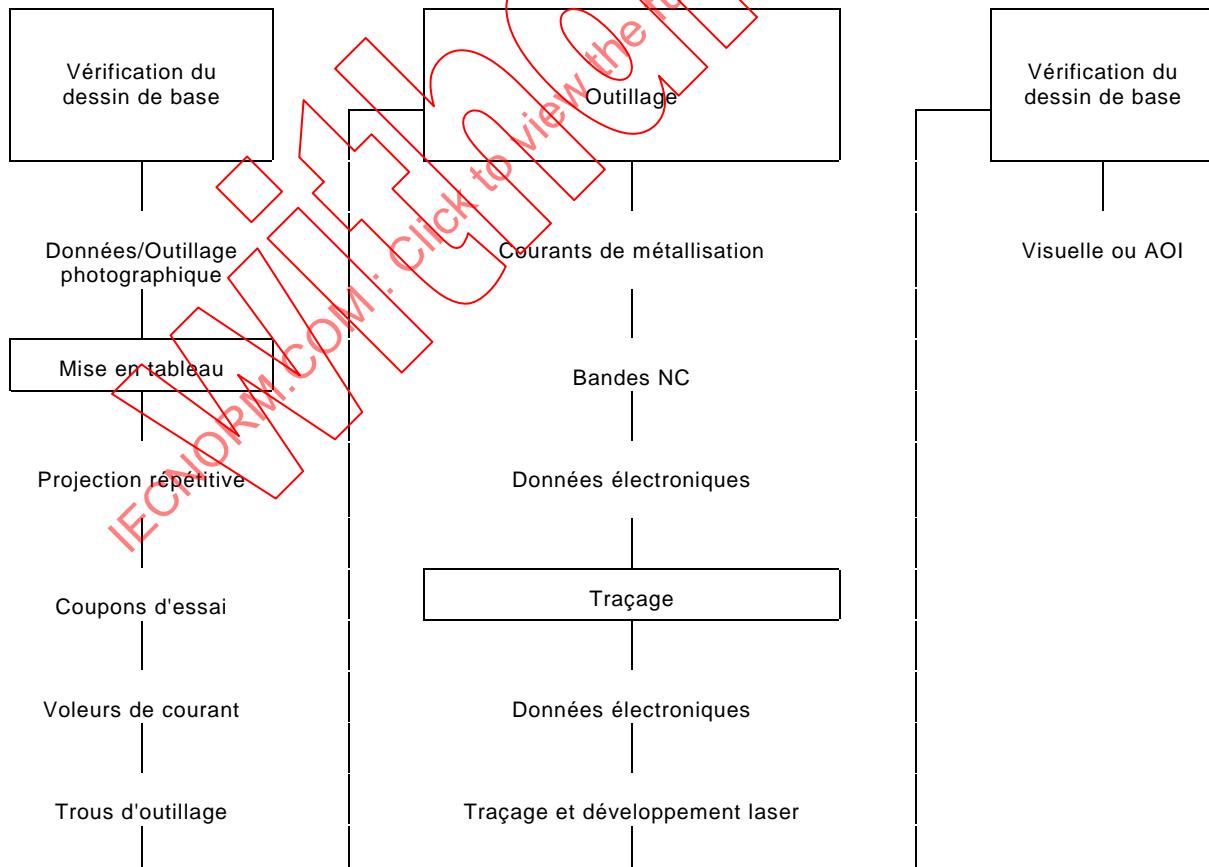

| 8.2 Processus de préproduction .....                                                            | 66    |

| 8.3 Processus de production .....                                                               | 70    |

| 8.4 Impact des défauts à haute fréquence .....                                                  | 74    |

| 8.5 Description de données .....                                                                | 78    |

| 9 Essai de réflectométrie temporelle (TDR) .....                                                | 78    |

| 9.1 Justification .....                                                                         | 78    |

| Annexe A – Unités, symboles et terminologie .....                                               | 82    |

## CONTENTS

|                                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

| FOREWORD .....                                                                      | 5    |

| INTRODUCTION .....                                                                  | 7    |

| Clause                                                                              |      |

| 1 Scope .....                                                                       | 9    |

| 2 Normative references .....                                                        | 9    |

| 3 Engineering design overview .....                                                 | 9    |

| 3.1 Device selection .....                                                          | 9    |

| 3.2 Intraconnection .....                                                           | 11   |

| 3.3 Printed board and printed board assemblies .....                                | 13   |

| 3.4 Performance requirements .....                                                  | 17   |

| 3.5 Power distribution .....                                                        | 37   |

| 4 Design of controlled impedance circuits .....                                     | 39   |

| 4.1 Configurations .....                                                            | 39   |

| 4.2 Equations .....                                                                 | 41   |

| 4.3 Controlled impedance design rules .....                                         | 47   |

| 4.4 Cross-talk rules .....                                                          | 49   |

| 4.5 Coupon design rules .....                                                       | 51   |

| 4.6 Decoupling/capacitor rules .....                                                | 55   |

| 5 Design for manufacturing .....                                                    | 59   |

| 5.1 Process rules in CAD .....                                                      | 59   |

| 5.2 Design complexity and correlation to cost .....                                 | 59   |

| 6 Data description .....                                                            | 59   |

| 6.1 Details of construction .....                                                   | 61   |

| 6.2 Isolation of data by net class (noise, timing, capacitance and impedance) ..... | 61   |

| 6.3 Electrical performance .....                                                    | 63   |

| 7 Material .....                                                                    | 63   |

| 7.1 Resin systems .....                                                             | 63   |

| 7.2 Reinforcements .....                                                            | 63   |

| 7.3 Prepregs, bonding layers and adhesives .....                                    | 65   |

| 7.4 Frequency dependence .....                                                      | 65   |

| 8 Fabrication .....                                                                 | 65   |

| 8.1 General .....                                                                   | 65   |

| 8.2 Preproduction processes .....                                                   | 67   |

| 8.3 Production processes .....                                                      | 71   |

| 8.4 Impact of defects at high frequencies .....                                     | 75   |

| 8.5 Data description .....                                                          | 79   |

| 9 Time domain reflectometry (TDR) testing .....                                     | 79   |

| 9.1 Rationale .....                                                                 | 79   |

| Annex A – Units, symbols, and terminology .....                                     | 83   |

## COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

**CARTES IMPRIMÉES ET CARTES IMPRIMÉES ÉQUIPÉES –

CONCEPTION ET UTILISATION –****Partie 1-2: Prescriptions génériques –

Impédance contrôlée****AVANT-PROPOS**

- 1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales. Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

- 2) Les décisions ou accords officiels de la CEI concernant les questions techniques, représentent, dans la mesure du possible un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés sont représentés dans chaque comité d'études.

- 3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés comme normes, rapports techniques ou guides et agréés comme tels par les Comités nationaux.

- 4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale correspondante doit être indiquée en termes clairs dans cette dernière.

- 5) La CEI n'a fixé aucune procédure concernant le marquage comme indication d'approbation et sa responsabilité n'est pas engagée quand un matériel est déclaré conforme à l'une de ses normes.

- 6) L'attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire l'objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 61188-1-2 a été établie par le comité d'études 52 de la CEI: Circuits imprimés.

Le texte de cette norme est issu des documents suivants:

| FDIS        | Rapport de vote |

|-------------|-----------------|

| 52/758/FDIS | 52/762/RVD      |

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant abouti à l'approbation de cette norme.

L'annexe A est donnée uniquement à titre d'information.

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

**PRINTED BOARDS AND PRINTED BOARD ASSEMBLIES –

DESIGN AND USE –****Part 1-2: Generic requirements –

Controlled impedance****FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61188-1-2 has been prepared by IEC technical committee 52: Printed circuits.

The text of this standard is based on the following documents:

| FDIS        | Report on voting |

|-------------|------------------|

| 52/758/FDIS | 52/762/RVD       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

Annex A is for information only.

## INTRODUCTION

L'encapsulation du matériel électronique a traditionnellement fait l'objet de considérations mécaniques. La conception de l'encapsulation présente une complexité croissante tandis que les techniques électroniques actuelles offrent une vitesse de commutation et une densité d'intégration plus élevées. Les puces individuelles possèdent un plus grand nombre de connexions pour des tailles de boîtier de puce plus réduites. Afin de tirer le meilleur avantage de la densité et de la vitesse du dispositif, il faut que les concepteurs accordent beaucoup plus d'attention aux problèmes posés par les phénomènes de propagation d'ondes électromagnétiques associés à la transmission de signaux de commutation au sein du système. De nouvelles disciplines et stratégies de conception sont nécessaires. Les cartes de circuit à impédance contrôlée s'inscrivent dans le cadre de cette stratégie.

L'interconnexion et l'encapsulation de composants électroniques relevaient principalement du domaine des concepteurs en mécanique qui se préoccupaient de facteurs tels que le poids, le volume, la puissance et le facteur de forme, les interconnexions étant spécifiées dans des listes de câblage ou listes de filet. Le routage des signaux pour conducteurs électriques était réalisé sans autres préoccupations que celle du maintien de la continuité entre les points, de la présence de cuivre en quantité suffisante dans les conducteurs pour le passage du courant et du respect du dégagement afin d'empêcher une rupture de tension. Les performances électriques du signal devaient garantir la qualité du trajet électrique, mais ne constituaient pas une préoccupation majeure.

Les progrès réalisés dans le domaine des circuits intégrés numériques font apparaître de nouveaux dispositifs offrant des temps de montée extrêmement rapides intégrés à des boîtiers microélectroniques à forte densité. Afin d'optimiser les performances du système, ces dispositifs nécessitent des techniques de câblage permettant des interconnexions à forte densité tout en offrant des performances électriques supérieures.

De nombreux problèmes de système sont associés au traitement numérique rapide, mais aucun n'a fait l'objet d'autant d'attention, récemment, que l'interconnexion. Il est évident que lorsque les vitesses de système augmentent, l'interconnexion, l'encapsulation et les cartes à circuit représentent les goulets d'étranglement responsables du ralentissement des performances du système. Les systèmes utilisant un circuit 100 K ECL subissent un ralentissement de presque 55 % au niveau de l'encapsulation et de l'interconnexion. Le CMOS est normalement considéré comme une technique «lente», mais elle s'intègre à des fréquences d'horloge dépassant 100 MHz. Dans ces cas, non seulement le retard du système constitue un problème, mais la question de l'affaiblissement du signal se pose au niveau des dispositifs BiCMOS à faible puissance, à faible tension et présentant une marge de bruit inférieure.

## INTRODUCTION

Packaging of electronic equipment has traditionally been an area for mechanical considerations. Packaging design is becoming more complex as today's electronics technologies are available in greater switching speed and higher density per chip. Individual chips have greater numbers of connections in smaller chip package sizes. To take maximum advantage of device density and speed, designers must pay much more attention to problems of electromagnetic wave propagation phenomena associated with transmission of switching signals within the system. New design disciplines and design strategies are needed. Controlled impedance printed boards are a part of this strategy.

Interconnection and the packaging of electronic components primarily have been the domain of mechanical designers who were concerned with such factors as weight, volume, power, and form factor and with interconnections specified in wire listing or net lists. Electrical conductors for signal transmission were routed with only a few concerns, that continuity was maintained between points, conductors had sufficient copper for the current and clearance was maintained to prevent voltage breakdown. Aside from providing a good electrical path, the electrical performance of the signal was not a major concern.

Advances in digital integrated circuits introduce new devices with extremely fast rise times which are housed in high density microelectronic packages. In order to optimize system performance, these devices require a wiring technology that supports high density interconnection and, at the same time, provides superior electrical performance.

While many system problems are associated with high speed digital processing, none has received more attention than interconnection. It is evident that as system speeds increase, interconnection, packaging, and printed boards become the bottlenecks that slow system performance. Systems using 100 K ECL circuitry have almost 55 % of the system delay in the packaging and interconnect. CMOS is normally considered a "slow" technology, but is designed into system clock rates in excess of 100 MHz. In these cases, not only is system delay a problem but signal attenuation becomes an issue with the low powered, low voltage, lower noise margin BiCMOS devices.

IECNORM.COM Click to visit

## CARTES IMPRIMÉES ET CARTES IMPRIMÉES ÉQUIPÉES – CONCEPTION ET UTILISATION –

### Partie 1-2: Prescriptions génériques – Impédance contrôlée

#### 1 Domaine d'application

La présente partie de la CEI 61188 est destinée à être utilisée par les concepteurs de circuit, les ingénieurs en encapsulation, les fabricants de cartes imprimées et le personnel responsable de l'approvisionnement, de façon que tous aient une appréhension commune de chaque domaine. L'objectif de l'encapsulation consiste à transférer un signal d'un dispositif à un ou plusieurs autres dispositifs au travers d'un conducteur. Les conceptions rapides sont définies comme des conceptions dont les propriétés d'interconnexion influent sur les performances du circuit et exigent des considérations particulières.

#### 2 Références normatives

Les documents normatifs suivants contiennent des dispositions qui par suite de la référence qui y est faite, constituent des dispositions valables pour la présente partie de la CEI 61188. Au moment de la publication, les éditions indiquées étaient en vigueur. Tout document normatif est sujet à révision, et les parties prenantes aux accords fondés sur la présente partie de la CEI 61188 sont invitées à rechercher la possibilité d'appliquer les éditions les plus récentes des documents normatifs indiqués ci-après. Les membres de la CEI et de l'ISO possèdent le registre des Normes internationales en vigueur.

CEI 61182 (toutes les parties), *Cartes imprimées – Description et transmission de données informatiques*

CEI 61182-1:1994, *Cartes imprimées – Description et transmission de données informatiques – Partie 1: Descriptif de carte imprimée sous forme numérique*

CEI 61189-3:1997, *Méthodes d'essai pour les matériaux électriques, les structures d'interconnexion et les ensembles – Partie 3: Méthodes d'essais des structures d'interconnexion (cartes imprimées)*

#### 3 Vue d'ensemble de la conception technique

##### 3.1 Sélection du dispositif

Parmi les options technologiques du dispositif figurent les TTL, Schottky TTL, CMOS, ECL et GaAs, chacune possédant ses propres prescriptions de puissance, gamme de températures de fonctionnement, densité de puce, impédance d'entrée, de sortie, niveaux de seuil de signal, sensibilité au bruit, temps de réponse et temps de montée/descente d'impulsions de sortie. De nombreuses conceptions intégreront des techniques mixtes, mélangeant la SMT et l'encapsulation par trous de liaison à la logique TTI, CMOS et ECL susceptibles de nécessiter des largeurs de ligne multiples (valeurs d'impédance) sur la même couche de circuit ou de faire un compromis sur une seule largeur de conducteur offrant suffisamment de marge aux différentes familles de logiques.

## PRINTED BOARDS AND PRINTED BOARD ASSEMBLIES – DESIGN AND USE –

### Part 1-2: Generic requirements – Controlled impedance

#### 1 Scope

This part of IEC 61188 is intended to be used by circuit designers, packaging engineers, printed board manufacturers and procurement personnel so that all may have a common understanding of each area. The aim in packaging is to transfer a signal from one device to one or more other devices through a conductor. High-speed designs are defined as designs in which the interconnecting properties affect circuit performance and require unique considerations.

#### 2 Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this part of IEC 61188. At the time of publication, the editions indicated were valid. All normative documents are subject to revision, and parties to agreements based on this part of IEC 61188 are encouraged to investigate the possibility of applying the most recent editions of the normative documents listed below. Members of IEC and ISO maintain registers of currently valid international standards.

IEC 61182 (all parts), *Printed boards – Electronic data description and transfer*

IEC 61182-1:1994, *Printed boards – Electronic data description and transfer – Part 1: Printed board description in digital form*

IEC 61189-3:1997, *Test methods for electrical materials, interconnection structures and assemblies – Part 3: Test methods for interconnection structures (printed boards)*

#### 3 Engineering design overview

##### 3.1 Device selection

Device technology options include TTL, Schottky TTL, CMOS, ECL and GaAs, each with its own set of power requirements, operating temperature range, density of chip, input impedance, output impedance, signal threshold levels, noise sensitivity, response time and output pulse rise/fall time. Many designs will have mixed technology where SMT and through hole packaging is intermixed with TTL, CMOS and ECL logic that may require multiple line widths (impedance values) on the same circuit layer or may compromise on a single conductor width that can provide enough margin for the different logic families.

Les puces peuvent être montées individuellement sur une grande carte ou assemblées sur de petites cartes ou modules multipuces montés sur de grandes cartes. Il n'est pas exclu que les systèmes de grande taille nécessitent plusieurs ensembles de grandes cartes présentant un autre niveau d'interconnexion. Le bruit, la temporisation et la dégradation du signal accompagneront les transitions d'un niveau d'encapsulation à un autre.

Les connexions électriques sur la carte peuvent présenter toute une gamme de configurations: broches de raccordement s'insérant dans la carte par des trous métallisés, comme dans les boîtiers à deux rangées de broches, série de pastilles dans le cas des dispositifs pour montage en surface. Les prescriptions relatives à l'encapsulation des composants dépendent de plusieurs facteurs, entre autres l'espace, l'économie, les performances électriques et la fiabilité, ainsi que le style d'encapsulation prédominant de l'ensemble. Les composants doivent offrir un style compatible avec les processus d'assemblage utilisés pour la fabrication de la carte imprimée équipée.

Le boîtier du composant doit être pris en compte lorsqu'on envisage une conception rapide. Au niveau des composants passifs, le facteur prédominant sera la longueur de la sortie car les sorties fournissent une inductance et une capacité supplémentaires influençant la vitesse de propagation et les transitoires de commutation. Pour minimiser ces effets, il est admis de réduire au maximum la longueur des sorties ou de les enlever. Les dispositifs pour montage en surface peuvent présenter des boîtiers sans sorties pouvant être directement montés sur le substrat d'interconnexion.

NOTE – Les fiches techniques de composants n'indiquent souvent pas de valeurs parasites concernant le bruit à vitesse rapide et la vitesse de propagation.

Les dispositifs actifs, les composants tels que les circuits intégrés, sont souvent proposés dans plusieurs boîtiers différents. En général, les boîtiers DIP, en plastique ou en céramique, sont les plus courants. Ce sont typiquement les plus grands et ceux qui fournissent l'environnement de fonctionnement rapide le moins bon du fait de la configuration des sorties. Le style de boîtier qui vient en second est le boîtier pour montage en surface. Ils sont proposés dans une gamme de boîtiers différents tels que SOIC, PLCC, PFQP ou TSOP. Ces boîtiers réduiront typiquement la capacité et l'inductance des sorties.

Pour obtenir des performances optimales au niveau du dispositif, la puce peut être directement montée sur le substrat en utilisant le pastillage (COB), la puce à bosses ou le soudage automatisé sur bande (TAB). Elles constituent une approche optimale car elles minimisent la capacité/inductance de sortie.

### **3.2 Intraconnexion**

#### **3.2.1 Connecteurs**

Les intraconnexions sont souvent sources de problèmes en application rapide car aucun environnement de signal continu n'est fourni. La plupart des systèmes de connecteurs carte à carte ne sont pas conçus pour une utilisation dans le cadre d'applications à hautes performances et compromettent l'intégrité de signal du système. Les connexions carte à carte présentent souvent un défaut d'adaptation de l'impédance caractéristique dans la carte elle-même.

Il existe deux approches principales pour réduire la discontinuité de signal provoquée par les systèmes d'interconnexion:

- a) la première approche consiste à fournir un style de connecteur permettant de disposer les brochages de manière à obtenir un trajet de signal satisfaisant. Les signaux non-différentiels doivent se définir par une référence située entre la ligne de signal active et la connexion du plan de référence le plus proche, qu'il s'agisse d'une tension ou d'un plan de masse. Les conducteurs de signaux non différentiels reposent sur des géométries contrôlées et un plan de référence proche pour le contrôle de l'impédance. La qualité de la broche de signal, celle de la broche de référence et leur emplacement déterminent les performances électriques. Pour optimiser les performances, des broches de référence doivent être ajoutées afin de réduire les problèmes de diaphonie. Généralement un rapport broche de signal-broche de référence de 3 à 1 est suffisant;

Chips can be individually mounted on a large board or assembled into small boards or multichip modules mounted onto large boards. Large systems may require several large board assemblies with another level of interconnection. Noise, timing, and signal degradation will accompany transitions from one packaging level to the next.

The electrical connections to the board can be of a variety of configurations ranging from pins that will insert through plated holes in the board, as in dual in-line packages, to a series of lands for surface mount devices. Requirements for component packaging are dependent on many factors including space, economics, electrical performance and reliability, as well as the predominant packaging style of the assembly. The components shall be provided in a style that is compatible with the assembly processes used to manufacture the printed board assembly.

The component package shall be considered when designing for high speed. In passive components the predominant factor will be the lead length as leads provide additional inductance and capacitance that will affect propagation speed and switching transients. To minimize these effects the leads may be as short as possible or removed. Surface mount devices can provide leadless packages which can be directly mounted to the interconnecting substrate.

NOTE – Component data sheets often do not provide parasitic values for high speed noise and propagation speed consideration.

Active devices, components such as integrated circuits, are often offered in several packages. In general, DIP packages, in either plastic or ceramic, have been the predominate package. These are typically the largest packages and provide the poorest high speed operating environment due to lead configuration. The next best package style is the surface mount package. These are offered in a variety of packages such as SOICs, PLCCs, PQFPs, TSOPs BGAs. These packages will typically reduce the lead capacitance and inductance.

To obtain the optimum performance from the device, the die can be directly mounted to the substrate using either the chip-on-board (COB), flip chip or tape automated bonding (TAB) approach. These offer an optimum approach since they minimize the lead capacitance/inductance.

### **3.2 Intraconnection**

#### **3.2.1 Connectors**

Intraconnections are often troublesome in high speed application because a continuous signal environment is not provided. Most board to board connector systems are not designed for use in high performance applications and compromise the signal integrity of the system. Board to board connections often mismatch the characteristic impedance designed into the board themselves.

There are two primary approaches to reduce the signal discontinuity caused by interconnect systems:

- a) The first approach is to provide a connector style such that the pinouts can be arranged to provide a good signal path. Non-differential signals shall establish a relationship between the active signal line and the closest reference plane connection, either a voltage or ground plane. Non-differential signal conductors rely on controlled geometries and nearby reference plane for impedance control. Signal pin quality, reference pin quality and their location controls electrical performance. To optimise performance, reference pins shall be added to reduce the cross-talk problems. Generally a 3:1 ratio of signal to reference pins (i.e. 3 signal, 1 reference) is sufficient;

- b) la seconde approche consiste à modifier le connecteur pour minimiser la distance de discontinuité entre les cartes. En diminuant la longueur de la broche, ou en ajoutant un plan de masse de référence dans le connecteur, on peut utiliser des distances plus réduites.

Des connecteurs coaxiaux montés sur carte sont fréquemment utilisés quand seules quelques lignes de signal sont connectées à une carte à circuit ou quand l'isolation ou l'intégrité du signal est importante.

### 3.2.2 Câbles

Des connecteurs et des câbles coaxiaux discrets sont souvent utilisés car ils peuvent coupler des signaux rapides, de haute fréquence, à une carte imprimée avec une faible dégradation de signal. Quatre domaines doivent être considérés:

- vitesse de propagation du signal;

- diaphonie;

- bruit induit;

- adaptation des impédances.

Des fils coaxiaux discrets ont été utilisés avec des cartes à fils discrets pour des applications rapides uniques jusqu'à 18 GHz. Un câble optique a également été utilisé avec succès avec des cartes à fils discrets pour des signaux à haute fréquence.

## 3.3 Cartes imprimées et cartes imprimées équipées

Le placement des composants est un facteur critique dans la conception de systèmes rapides. Les effets d'un placement inadapté peuvent être importants et affectent les domaines suivants:

- gestion de la diaphonie;

- contrôle de l'impédance;

- répartition de la puissance.

### 3.3.1 Conception de la carte

Le nombre de couches du signal dans les cartes multicouches sera influencé par la densité des interconnexions au sein de la carte ainsi que l'effet de la diaphonie ou du couplage entre les lignes de signal. La tolérance au niveau de la diaphonie peut rendre nécessaire d'ajouter des couches ou d'exiger une augmentation de l'espace entre les conducteurs, réduisant ainsi la densité d'interconnexion.

La densité des interconnexions des cartes à fils discrets influencera l'effet de diaphonie. Il n'est pas exclu que l'utilisation d'un routage de fil diagonal sur les mêmes couches de câblage qui roulent les conducteurs verticalement ou horizontalement (c'est-à-dire directions X et Y) permette une plus grande densité de circuit par couche et que les géométries de placement disponibles puissent permettre une densité élevée et une faible diaphonie.

Il existe une relation étroite entre la conception et les performances dans le cas de lignes d'interconnexion impliquant des signaux numériques rapides. Cette interdépendance n'existe pas auparavant ou pouvait être ignorée dans les applications de signaux lents, cependant elle impose maintenant de nouvelles règles de conception, restrictions et gestions de processus.

Pour relever les défis posés par le traitement numérique rapide, la carte imprimée multicouche actuelle doit:

- réduire le temps de propagation;

- réduire la diaphonie et les autres parasites de ligne;

- réduire la perte de signal;

- permettre les interconnexions à densité élevée.

- b) The second approach is to modify the connector to minimize the discontinuity. By shortening the pin length, or adding a reference ground plane within the connector, smaller distances between boards can be used.

Board mounted coaxial connectors are frequently used when only a few signal lines are connecting to a circuit board or where either signal isolation or signal integrity is important.

### 3.2.2 Cables

Discrete coax connectors and cables are often used because they can couple high speed, high frequency signals to a printed board with little signal degradation. There are four areas that shall be considered:

- signal propagation speed;

- cross-talk;

- induced noise;

- impedance matching.

Discrete coaxial wires have been used with discrete wiring boards for unique, high-speed applications up to 18 GHz. An optical cable has also been used successfully with discrete wiring boards for high frequency signals.

## 3.3 Printed board and printed board assemblies

Component placement is a critical factor in the design of high-speed systems. The effects of unsuitable placement can be significant and include concerns in the following areas:

- cross-talk management;

- impedance control;

- power distribution.

### 3.3.1 Board design

The number of signal layers in multilayer boards will be influenced by the density of interconnections within the board as well as the effect of cross-talk or coupling between signal lines. Cross-talk allowance can make it necessary to add layers or can require increasing space between conductors decreasing the interconnect density.

Discrete wiring board density of interconnections within the board will influence the effect of cross-talk. The use of diagonal wire routing on the same wiring layers that route conductors vertically or horizontally (i.e. X and Y directions) may allow greater circuit density per layer and the placement geometries available can accommodate high density and low cross-talk.

A close relationship between design and performance exists in the case of interconnection lines involving high speed digital signals. This interdependence did not exist previously or could be ignored in low-speed signal applications, however, it now imposes new design rules, restrictions and process controls.

To meet the challenges of high-speed digital processing, today's multilayer printed board shall:

- reduce propagation delay;

- lower cross-talk and other line parasitics;

- reduce signal loss;

- allow for high density interconnections.

Pour atteindre les objectifs souhaités, le concepteur doit commencer par contrôler l'impédance des lignes de transmission.

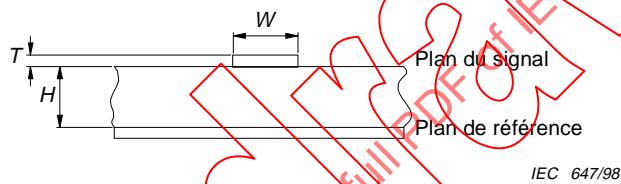

Les conducteurs contrôlés sur les cartes peuvent être utilisés pour l'interconnexion de signaux entre dispositifs. Pour une construction donnée, l'impédance peut être contrôlée avec une épaisseur diélectrique, une épaisseur et une largeur de conducteur spécifiques ainsi que la permittivité relative (constante diélectrique).

La sélection du substrat de la carte, la permittivité relative (constante diélectrique) ( $\epsilon_r$ ) affecte la propagation du signal et l'épaisseur pour une impédance caractéristique donnée ainsi qu'une largeur de ligne donnée. Une permittivité relative  $\epsilon_r$  inférieure accélère la propagation du signal mais augmente la largeur du conducteur pour une valeur d'impédance donnée.

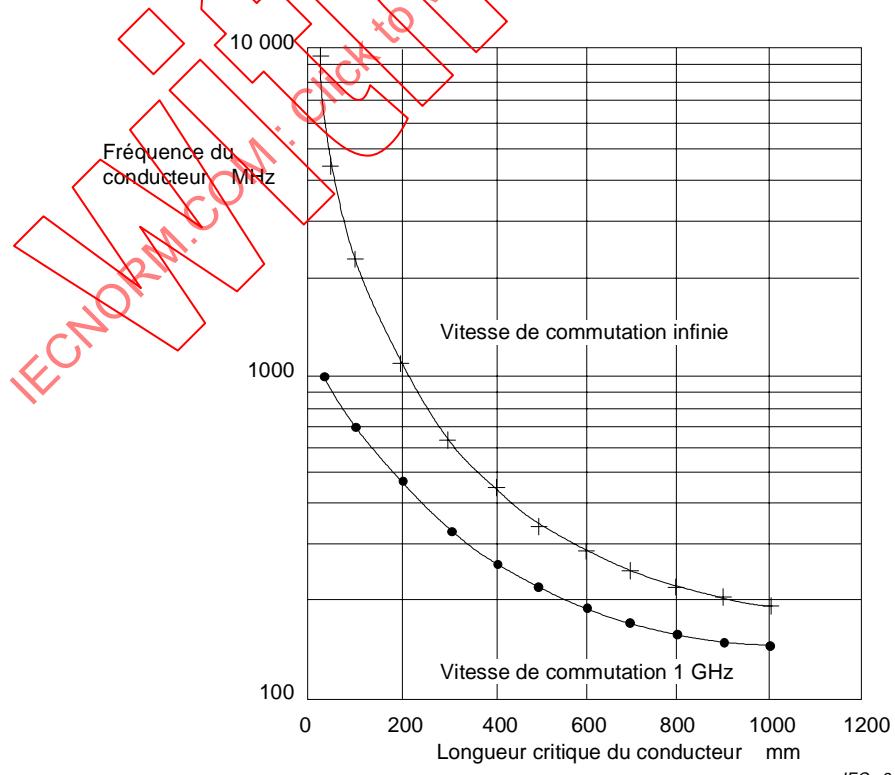

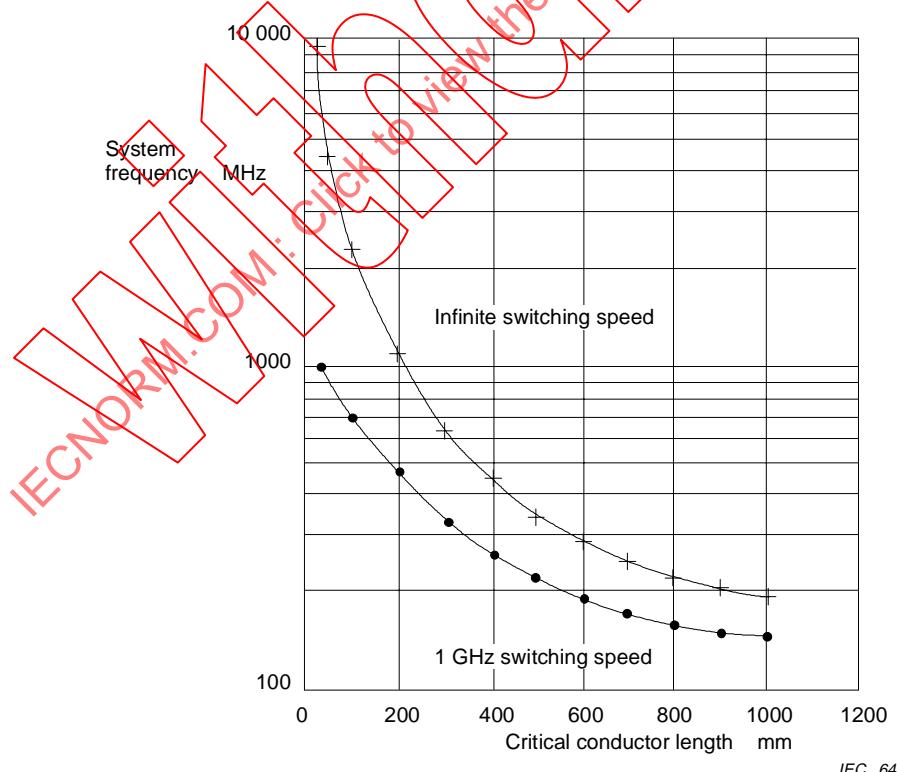

Pour les cartes à fils discrets, l'épaisseur et la largeur du conducteur sont contrôlées en sélectionnant la taille de fil appropriée. L'isolation de fils discrets peut occasionner une diminution de la permittivité relative effective (constante diélectrique) pour une construction donnée, provoquant une augmentation des vitesses de propagation de signal au niveau des cartes à fils discrets. Une conception réalisée en fonction de valeurs d'impédance spécifiques contrôle (comme les lignes de transmission) la capacité et le matériau entre les conducteurs. Il convient de maintenir des trajets de signaux courts pour minimiser les temps de propagation. Même s'il était possible de créer un circuit capable de commuter à une vitesse infinie, le matériau d'interconnexion dicterait les performances des systèmes. La figure 1 illustre la vitesse de commutation d'un dispositif par rapport au temps de propagation d'un diélectrique typique en tissu de verre/époxy couramment utilisé dans l'industrie des cartes imprimées.

Les contraintes spatiales, le nombre et la complexité des interconnexions, la répartition de la puissance et le coût de fabrication représentent une partie des facteurs à considérer. Pour déterminer les prescriptions relatives aux couches, il faut prendre en compte l'épaisseur des couches diélectriques, la composition et l'épaisseur des couches de plan de masse/de tension, la composition diélectrique, la largeur/l'épaisseur du conducteur et la longueur totale. La largeur et l'épaisseur du conducteur détermineront les coûts de fabrication.

Figure 1 – Vitesse de commutation par rapport au temps de propagation

To achieve these desired goals the designer shall start by controlling the impedance of the transmission lines.

Controlled conductors on boards can be used for signal interconnect between devices. For a given construction, impedance can be controlled with a specific dielectric thickness, conductor thickness, conductor width and the relative permittivity (dielectric constant).

Board substrate selection, relative permittivity (dielectric constant) ( $\epsilon_r$ ) effects signal propagation and thickness for a given characteristic impedance as well as line width. Lower  $\epsilon_r$  results in faster signal propagation, but increases conductor width for a given impedance value.

For discrete wired boards the conductor thickness and width is controlled by selection of the appropriate wire size. The insulation on the discrete wires can result in a lower effective relative permittivity (dielectric constant) for a given construction, resulting in higher signal propagation speeds in discrete wire boards. Designing to specific impedance values, controls (as transmission lines) the capacitance and the material between conductors. Signal paths should be kept short to minimize propagation delays. Even if it were possible to make a circuit capable of switching at infinite speed, the interconnection material would dictate the performance of the systems. Figure 1 illustrates the switching speed of a device versus propagation delay in a typical woven glass epoxide dielectric commonly used in the printed board industry.

Space constraints, number and complexity of interconnections, power distribution and cost of manufacture are some factors to be considered. When determining requirements of layer count the thickness of dielectric layers, the composition and thickness of ground/voltage plane layers, the dielectric composition, conductor width/thickness and the overall length. The width and thickness of the conductor will determine manufacturing costs.

Figure 1 – Switching speed versus propagation delay

### 3.4 Prescriptions de performance

La théorie de propagation des ondes électromagnétiques doit être considérée en évaluant les performances de l'interconnexion et de ses substrats. Les dispositifs rapides se caractérisent par un temps réduit de montée des impulsions dont la forme d'onde est similaire à un signal sinusoïdal alternatif. Quand le temps de montée de l'impulsion diminue, la fréquence de la forme d'onde augmente et la carte imprimée ressemble de plus en plus à un circuit rapide à courant alternatif.

#### 3.4.1 Répartition de la puissance

Pour les dispositifs rapides, l'activité de commutation s'accompagne d'exigences de changements tout aussi rapides du courant électrique au niveau de l'alimentation. Si plusieurs dispositifs demandent du courant à peu près au même instant, il est nécessaire que le système de répartition de la puissance réponde à ces exigences tout en maintenant sa tension. Cette prescription requiert l'établissement de connexions à faible inductance aux dispositifs à forte capacité pour les différentes tensions du système.

#### 3.4.2 Permittivité relative (constante diélectrique)

La permittivité relative,  $\epsilon_r$ , d'une substance, est définie comme le rapport de la permittivité du matériel et de la permittivité en espace libre, qui possède une valeur de 1,00. La permittivité relative (constante diélectrique) est le terme couramment utilisé dans l'industrie bien que la constante diélectrique varie selon plusieurs paramètres. Parmi les facteurs influençant la permittivité relative (constante diélectrique) d'un matériau donné, on distingue la fréquence électrique à laquelle la mesure est effectuée, ainsi que la température et l'ampleur de l'absorption d'eau. En outre, si le matériau est un composite, c'est-à-dire un stratifié renforcé, on admet que la valeur de  $\epsilon_r$  varie énormément lorsqu'on modifie la quantité relative de chaque composant du composite.

La permittivité relative (constante diélectrique),  $\epsilon_r$  du diélectrique d'une structure d'interconnexion affectera les performances électriques. Le choix de  $\epsilon_r$  est utilisé au niveau de la conception de la structure afin de respecter les prescriptions relatives à l'impédance, la capacité et le temps de propagation du système. Pour une géométrie de ligne conductrice donnée, le temps de propagation variera directement comme la racine carrée de  $\epsilon_r$ , l'impédance inversement à la racine carrée de  $\epsilon_r$  et la capacité directement comme  $\epsilon_r$ .

La permittivité relative effective (constante diélectrique),  $\epsilon'_r$ , est la permittivité relative expérimentée par un signal électrique transmis le long d'un trajet conducteur. Il est permis d'obtenir une valeur expérimentale de  $\epsilon_r$  en utilisant une technique de réflectométrie temporelle (TDR).

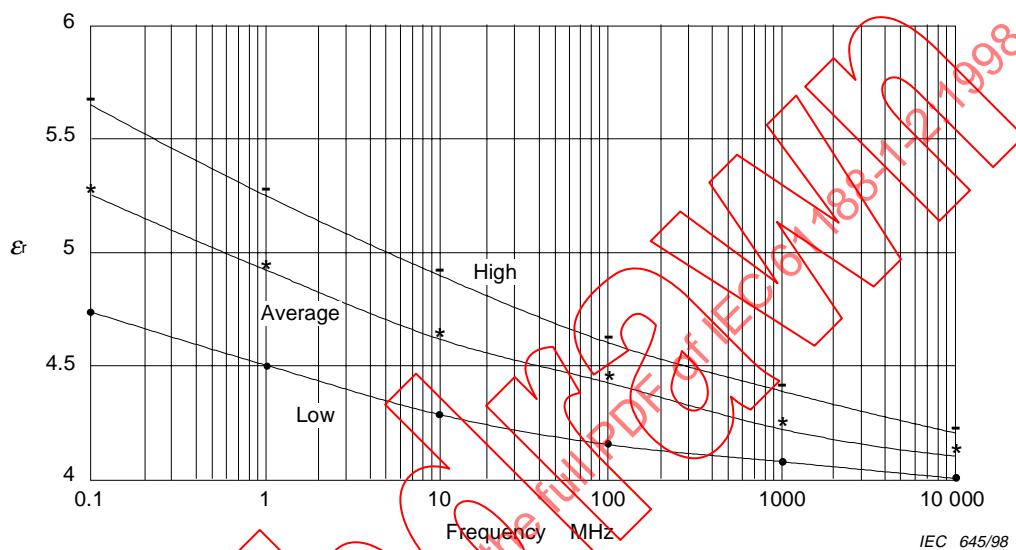

#### 3.4.3 Relation entre la permittivité relative (constante diélectrique) et la fréquence

Les valeurs de  $\epsilon_r$  et  $\epsilon'_r$  dépendent toutes deux du rapport renforcement-résine, de la température, de l'absorption d'eau et de la fréquence à laquelle la mesure est effectuée. Il est permis de prendre des mesures afin d'assurer que les mesures électriques sont réalisées dans des conditions similaires à l'application finale.

Certains matériaux, tels qu'un stratifié verre/époxy, présentent une dépendance vis-à-vis de la fréquence des propriétés diélectriques du produit, et il devient important de choisir soigneusement la fréquence à laquelle les mesures sont faites. Sélectionner la fréquence de façon qu'il soit permis d'utiliser les paramètres diélectriques obtenus pour fournir une prédition précise des caractéristiques électriques de la carte imprimée finie.

La plupart des caractéristiques de transmission d'une carte imprimée étant déterminées par des mesures TDR, il est judicieux d'utiliser la fréquence correspondant à ces mesures TDR comme fréquence de choix pour la comparaison des propriétés diélectriques.

### 3.4 Performance requirements

Electromagnetic wave propagation theory shall be considered in evaluating the performance of the interconnection and their substrates. High-speed devices are characterized by the short rise time of the pulses whose wave form is similar to an a.c. sinusoidal signal. As the rise time of the pulse decreases, the frequency of the wave form increases and the printed board looks increasingly like a high-speed a.c. circuit.

#### 3.4.1 Power distribution

For high-speed devices, switching activity is accompanied by equally high-speed demands for changes in electrical current from the power supply. If several devices demand current at or near the same instant, the power distribution system is required to meet these demands while maintaining its voltage. This requirement demands low inductance connections to devices with high capacitance for the various voltages in the system.

#### 3.4.2 Relative permittivity (dielectric constant)

The relative permittivity,  $\epsilon_r$ , of a substance is defined as the ratio of the permittivity of the material to the permittivity of free space, which has a value of 1,00. Relative permittivity (dielectric constant) is the term in common use in industry even though dielectric constant varies with several parameters. Factors that influence the relative permittivity (dielectric constant) of a given material include the electrical frequency at which the measurement is performed, temperature, and extent of water absorption. In addition, if the material is a composite for example a reinforced laminate, the value of  $\epsilon_r$  may vary enormously as the relative amount of each component of the composite is changed.

The relative permittivity (dielectric constant),  $\epsilon_r$ , of the dielectric of an interconnecting structure will affect electrical performance. The choice of  $\epsilon_r$  is used in the design of the structure to meet the impedance, capacitance and propagation time requirements of the system. For a given conductor line geometry, propagation time will vary directly as the square root of  $\epsilon_r$ , impedance inversely as the square root of  $\epsilon_r$ , and capacitance directly as  $\epsilon_r$ .

The effective relative permittivity (dielectric constant),  $\epsilon'_r$ , is the relative permittivity that is experienced by an electrical signal transmitted along a conductive path. An experimental value of  $\epsilon'_r$  may be obtained using a time domain reflectometry (TDR) technique.

#### 3.4.3 Relative permittivity (dielectric constant) and frequency relationship

Values of both  $\epsilon_r$  and  $\epsilon'_r$  are dependent on the reinforcement to resin ratio, temperature, water uptake and the frequency at which the measurement is performed. Steps may be taken to ensure that electrical measurements are performed under conditions that are similar to the final application.

Some materials, such as an epoxide/glass laminate, exhibit a dependence of frequency component of dielectric properties, and it becomes important to choose carefully the frequency at which measurements are made. Select the frequency such that the dielectric parameters obtained may be used to provide a precise prediction of the electrical characteristics of the finished printed board.

Since most transmission characteristics for a printed board are determined by TDR measurements, it is appropriate to use the frequency corresponding to these TDR measurements as the frequency of choice for comparing dielectric properties.

Il est permis de déterminer la fréquence concernée ou la largeur de bande (BW) la plus élevée d'une impulsion numérique en gigahertz sur la base de cette relation:

$$BW = 0,35/t_r$$

où  $t_r$ , en nanosecondes, représente le temps de montée d'impulsion de 10 % à 90 % de sa valeur maximale. Ainsi, une impulsion TDR typique, avec un temps de montée de 100 ps, présente une largeur de bande de 3,5 GHz. (Une certaine dégradation de ce temps de montée survient cependant au niveau de la transmission du fait du montage d'essai, ce qui réduit quelque peu la fréquence effective). Cela impose que les mesures diélectriques réalisées par des méthodes autres que la TDR soient effectuées à haute fréquence.

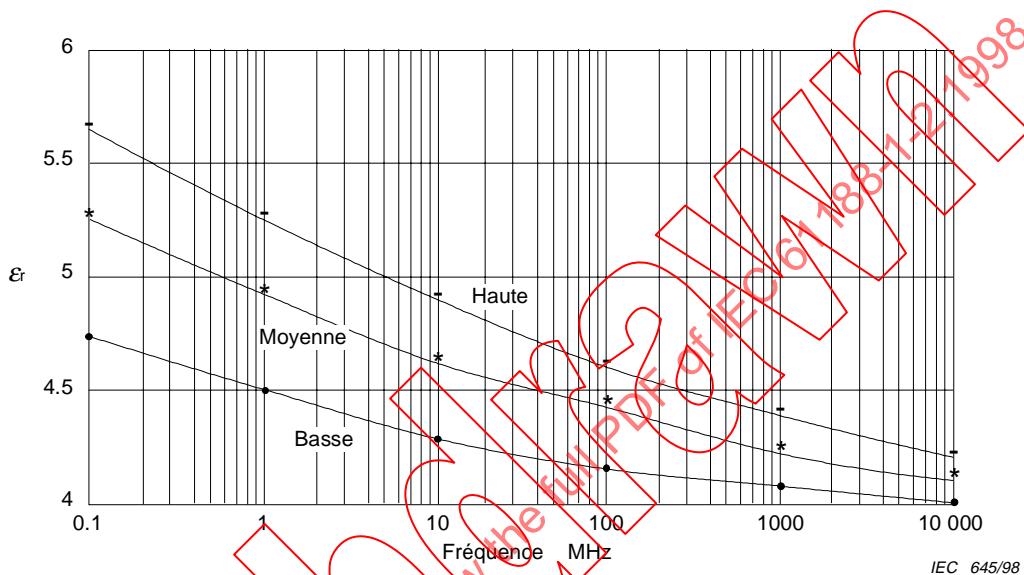

Figure 2 –  $\epsilon_r$  par rapport à la fréquence (stratifié verre/époxy)

L'équation permettant de prévoir la moyenne mondiale  $\epsilon_r$  est la suivante:

$$\epsilon_r = 4,97 - 0,257 [\log f / 10] \times 10^6$$

Une variation à trois sigma était mesurée à  $\pm 0,35$  (8 %).

Une  $\epsilon_r$  ligne à ligne à trois sigma sur un flan de carte imprimée était mesurée à  $\pm 0,26$  (6 %)

Comme indiqué auparavant,  $\epsilon_r$  est lié au rapport résine verre. La figure 2 représente une moyenne prise en compte.

Les prédictions  $Z_0$  correspondront de façon plus précise aux mesures TDR si une valeur de  $\epsilon_r$  de 4,1 est utilisée car les essais TDR sont réalisés à de très hautes fréquences.

$Z_0$  augmente à des fréquences inférieures à 1 MHz selon un taux plus élevé que prévu, ce qui est dû à un étalement sur le plan de référence.

The highest frequency of concern or bandwidth (BW) in gigahertz of a digital pulse may be obtained from the relationship:

$$BW = 0,35/t_r$$

where  $t_r$  in nanoseconds is the pulse rise time from 10 % to 90 % of its maximum value. Thus, a typical TDR pulse, with a rise time of 100 ps, has a bandwidth of 3,5 GHz. (Some degradation of this rise time, however, occurs in transmission through the test fixture, thus reducing the effective frequency somewhat.) This dictates that dielectric measurements made by methods other than TDR shall be conducted at higher frequency.

Figure 2 –  $\epsilon_r$  versus frequency (epoxide/glass laminate)

The equation to predict worldwide average  $\epsilon_r$  is:

$$\epsilon_r = 4,97 - 0,257 [\log f / 10] \times 10^6$$

Three sigma variation was measured at  $\pm 0,35$  (8 %).

Three sigma line to line  $\epsilon_r$  variation on a printed board panel was measured at  $\pm 0,26$  (6 %).

As previously stated,  $\epsilon_r$  is related to the resin to glass ratio. Figure 2 represents an average which takes that into account.

$Z_0$  predictions will more closely agree with TDR measurements if a value of  $\epsilon_r$  of 4,1 is used since TDR testing is done at very high frequencies.

$Z_0$  increases at frequencies below 1 MHz at a rate that is greater than expected. This is due to current spreading on the reference plane.

La figure 2 montre des tracés de  $\epsilon_r$  mesurés sur la gamme de fréquences de 100 kHz à 10 GHz, pour un stratifié de type stratifié verre/époxy avec un rapport verre-résine d'environ 40:60 selon le poids. La valeur de  $\epsilon_r$  pour ce stratifié varie environ de 4,7 à 4,0 sur cette gamme de fréquences. Ce changement de l'amplitude de  $\epsilon_r$  est principalement dû à la réponse en fréquence de la résine et se trouve donc réduit si la proportion de verre dans le composite augmente. En outre, la réponse en fréquence changera également si un système résineux de substitution est choisi. Les fournisseurs de matériaux citent généralement des valeurs de propriétés diélectriques déterminées à 1 MHz.

#### 3.4.4 Vitesse de signal critique

Selon la règle générale, les effets de la ligne de transmission (effets d'onde) représentent une considération de conception importante quand la longueur du conducteur se rapproche du 1/7 de la longueur d'onde du signal. Si la fréquence d'horloge est de 300 MHz, la longueur d'onde dans l'air est d'environ 1 m. Généralement, l'horloge du système est la répétition d'une impulsion de signaux carrés. La plupart des systèmes seront numériques, ainsi les données sont acheminées par le front de l'impulsion (montée très courte). Il doit être permis à ce front de monter (ou descendre) aussi vite que possible. La fréquence et le temps de montée du signal sont liés par la relation  $t_r = 0,35/f$ , où  $t_r$  représente le temps de montée en nanosecondes et  $f$  la fréquence en gigahertz.

Le tableau 1 indique les temps de montée pour certaines familles d'IC.

**Tableau 1 – Temps de montée du dispositif**

| Temps de montée du dispositif |                    |

|-------------------------------|--------------------|

| Famille de dispositifs        | Temps de montée ns |

| TTL                           | 6-9                |

| Schottky TTL                  | 2-3                |

| ECL                           | 0,45-0,75          |

| GaAs                          | 0,05-0,20          |

Par exemple ECL a un temps de montée de 0,45 ns avec une fréquence correspondante de 0,35/0,45 GHz ou 777 MHz. En utilisant la formule  $t_{pd} = \text{racine carrée de } \epsilon_r / c$  ( $t_{pd}$  est le temps de propagation,  $c$  est la vitesse de la lumière), on obtient une longueur d'onde dans l'air d'environ 375 mm, 190 mm en stratifié verre/époxy ou moins de 100 mm en céramique. Cela signifie que pour les cartes imprimées fabriquées en stratifié verre/époxy, si le trajet d'interconnexion dépasse 250 mm, il convient de prendre en compte les propriétés électromagnétiques du signal et les effets de ligne de transmission.

Par conséquent, la vitesse du signal critique correspond au temps de montée/descente du signal du dispositif au lieu de la fréquence d'horloge.

#### 3.4.5 Environnement de ligne capacitive par rapport à un environnement de ligne d'impédance contrôlée

La ligne conductrice peut être traitée soit par une ligne de transmission, soit par une ligne capacitive. Dans le cas des lignes de transmission, la règle de conception consiste à fournir une impédance caractéristique connue avec une impédance adaptée permettant de minimiser les réflexions résultant d'impulsions à temps de montée rapide. Dans le cas des lignes capacitatives, selon le concept, une ligne nécessite une certaine circulation de courant pour permettre un changement de tension détecté à destination. Les paramètres critiques et les prescriptions de conception dépendront du concept approprié.

Figure 2 shows plots of the  $\varepsilon_r$ , measured over the frequency range 100 kHz to 10 GHz, for an epoxide/glass type laminate with a glass-to-resin ratio of approximately 40:60 by weight. The value of  $\varepsilon_r$  for this laminate varies from about 4,7 to 4,0 over this frequency range. This change in the magnitude of  $\varepsilon_r$  is principally due to the frequency response of the resin and thus is reduced if the proportion of glass in the composite is increased. In addition, the frequency response will also be changed if an alternative resin system is selected. Material suppliers typically quote values of dielectric properties determined at 1 MHz.

### 3.4.4 Critical signal speed

The general rule is that transmission line effects (wave effects) become an important design consideration when the length of the conductor approaches 1/7 of the wave length of the signal. If the system clock frequency is 300 MHz, the wavelength in air is about 1 m. Generally, the system clock is a repetition of a square wave pulse. Most systems will be digital, so data are carried in the leading edge of the pulse (the sharp rise). This edge shall be permitted to rise (or fall) as quickly as possible. Frequency and the rise time of the signal are related by the relation  $t_r = 0,35/f$  where  $t_r$  is rise time in nanoseconds and  $f$  is the frequency in gigahertz.

Table 1 shows the rise times for some families of the ICs.

**Table 1 – Device rise time**

| Device rise time |              |

|------------------|--------------|

| Device family    | Rise time ns |

| TTL              | 6-9          |

| Schottky TTL     | 2-3          |

| ECL              | 0,45-0,75    |

| GaAs             | 0,05-0,20    |

For example, ECL has a rise of 0,45 ns time with a corresponding frequency of 0,35/0,45 GHz or 777 MHz. Using the formula  $t_{pd} = \sqrt{\varepsilon_r/c}$  ( $t_{pd}$  is the propagation delay,  $c$  is the speed of light), this translates to a wavelength in air of about 375 mm, 190 mm in epoxide/glass laminate or less than 100 mm in ceramic. This means that for printed boards fabricated from epoxide/glass laminate, if the interconnection path is more than 250 mm, the electromagnetic properties of the signal, and transmission line effects should be considered.

Therefore, the critical signal speed is the signal rise/fall time of the device instead of the clock frequency.

### 3.4.5 Capacitive line versus controlled impedance line environment

The conductor line can either be treated as a transmission line or a capacitive line. The design concept for transmission lines is to provide a known characteristic impedance with a matching impedance to minimize reflections resulting from fast rise time pulses. The concept for a capacitive line is that a line requires a certain amount of current flow to result in the changed voltage being detected at the destination. The critical design parameters and requirements will depend on which concept is appropriate.

### 3.4.5.1 Ligne capacitive

Quand on considère la ligne de signal comme une ligne capacitive, le temps de propagation est calculé en supposant que la ligne et les charges connectées sont purement capacitives. Les réflexions sur la ligne d'interconnexion courte surviennent plusieurs fois pendant le temps de montée de l'impulsion, le résultat net correspond à une dégradation du temps de transition de bord, c'est-à-dire un ralentissement, contrairement aux échelons distincts apparaissant sur les lignes de transmission. L'utilisation des équations relatives aux lignes de transmission fournit généralement un temps de propagation beaucoup plus rapide, créant par là-même un résultat imprécis.

### 3.4.5.2 Ligne d'impédance contrôlée

L'impédance caractéristique ( $Z_0$ ) du conducteur du circuit est analogue à la résistance d'un courant continu (donnée par la loi d'Ohm selon laquelle  $R = U/I$ ). Pour un circuit rapide, l'impédance est toujours le rapport de la tension d'attaque et du courant traversant le conducteur. La différence critique est la suivante: dans le cas de la haute fréquence, on s'intéresse au passage du courant durant la période de temps précédant le moment où le front de l'impulsion de tension atteint le dispositif.

L'impédance joue un rôle important dans la conception de la carte pour plusieurs raisons.

Si l'on applique la définition ci-dessus, la quantité de courant nécessaire à l'élément de circuit (amplificateur) pour suivre un trajet de signal dépend de  $Z_0$ . La conception d'IC en tient compte et elle peut influencer l'emplacement éventuel des récepteurs le long du circuit.

Au niveau des systèmes rapides présentant une discontinuité le long du trajet de signal, des réflexions surviendront. Les réflexions, non seulement réduisent la quantité de courant atteignant le récepteur, mais sont également susceptibles de provoquer une oscillation (bruit) le long du circuit. Ces formes de dégradation de signal peuvent provoquer des dysfonctionnements du système du fait de signaux manquants (résultant d'une perte de niveau d'affaiblissement) ou de signaux parasites (résultant du bruit des réflexions).

La période de temps de mesure étant très courte, la terminaison du circuit ne compense pas l'impédance caractéristique. De même, la résistivité du conducteur, généralement du cuivre, ne contribue pas de façon significative à l'impédance du circuit rapide. Ces deux effets sont dus au fait que le rapport de la tension d'attaque et du courant ( $U/I$  = impédance) est déterminé avant que le signal n'atteigne l'extrémité du circuit.

### 3.4.6 Largeur de bande

A partir des équations de Maxwell, il est possible de montrer que le temps de propagation pour un signal traversant un conducteur d'une carte imprimée/fil discret est le suivant:

$$t_{pd} = \sqrt{\frac{\epsilon_r}{c}}$$

A basse fréquence, il est généralement permis de représenter électriquement un trajet de signal sur une carte imprimée comme une capacité en parallèle avec une résistance. Cependant, quand la fréquence augmente, cette approche de modélisation de circuit à constantes localisées ne s'applique plus et les trajets de signaux doivent être considérés comme des lignes de transmission.

Pour l'interconnexion de conducteurs à impédance contrôlée, les propriétés électriques et diélectriques des matériaux de la carte présentent une importance plus grande et plus de soin doit être pris pour la conception et la terminaison du circuit. Plusieurs tentatives ont été faites pour définir le point à partir duquel les conducteurs agissent comme des lignes de

### 3.4.5.1 Capacitive line

When the signal line is considered as a capacitive line, the propagation time is calculated assuming the line plus the loads connected to it are purely capacitive. Because the reflections on the short interconnecting line occur several times during the pulse's rise time, the net result is a degradation of the edge transition time, i.e. slowing down, as opposed to distinct steps that occur in transmission lines. Using the transmission line equations generally provides a much faster propagation time, creating an inaccurate result.

### 3.4.5.2 Controlled Impedance line

The characteristic impedance ( $Z_0$ ) of the circuit conductor is analogous to the resistance of a d.c. (given by Ohm's law as  $R = U/I$ ). For a high speed circuit, the impedance is still the ratio of the driving voltage to the current that flows along the conductor. The critical difference is that in the high frequency case, one is interested in the current flow during the time period before the rising edge of the voltage pulse reaches the next device.

Impedance is important in board design for several reasons.

Applying the definition above, the amount of current that the circuit element (driver) will need to pass along a signal path depends on  $Z_0$ . This is taken into account in the design of ICs and can effect where receivers may be placed along the circuit.

In high-speed systems with discontinuity along the signal path, reflections will occur. Reflections not only reduce the amount of power reaching the receiver, but may also cause ringing (noise) along the circuit. These forms of signal degradation can cause systems to malfunction due to missing signals (from attenuation drop out) or spurious signals (from reflections noise).

Because the time period for measurement is very short, circuit termination does not offset the characteristic impedance. Likewise, the resistivity of the conductor, typically copper, does not contribute significantly to the high speed circuit impedance. Both of these effects are because the ratio of driving voltage to current ( $U/I$  = impedance) is determined before the signal reaches the end of the circuit.

### 3.4.6 Bandwidth

From Maxwell's equations, it can be shown that propagation time for a signal passing through a conductor in a discrete wiring/printed board:

$$t_{pd} = \sqrt{\frac{\epsilon_r}{c}}$$

At low frequencies, a signal path on a printed board may usually be represented electrically as a capacitance in parallel with a resistance. However, as the frequency is increased, this approach of lumped circuit modelling breaks down and signal paths shall be regarded as transmission lines.

For controlled impedance conductor interconnection, the electrical and dielectric properties of the board materials have increased importance and greater care shall be taken with the design and termination of the circuit. Several attempts have been made to define the point at which conductors act as transmission lines. The required analysis needs to be performed in either the

transmission. Il est nécessaire d'effectuer l'analyse requise soit au niveau de la fréquence, soit au niveau du domaine temporel. Cependant, le point critique à retenir pour les signaux numériques est le suivant: c'est le temps de montée de l'impulsion et non la fréquence d'horloge du dispositif qui représente le facteur déterminant. La fréquence d'horloge est un paramètre dépendant car plus le temps de montée est rapide, plus la fréquence d'horloge d'un dispositif peut augmenter.

**Tableau 2 – Données types pour certaines familles logiques**

| <b>Famille logique</b> | <b>Temps de montée</b><br>ns | <b>Largeur de bande</b><br>MHz | <b>Longueur d'onde dans l'espace libre</b> |                                         |                                               |

|------------------------|------------------------------|--------------------------------|--------------------------------------------|-----------------------------------------|-----------------------------------------------|

|                        |                              |                                | <b>Dans l'espace libre</b><br>m            | <b>Dans stratifié verre/époxy*</b><br>m | <b>1/2 montée stratifié verre/époxy*</b><br>m |

| TTL                    | 8,0                          | 44                             | 6,800                                      | 3,100                                   | 0,5500                                        |

| Schottky TTL           | 3,0                          | 120                            | 2,500                                      | 1,200                                   | 0,2100                                        |

| ECL                    | 0,6                          | 580                            | 0,520                                      | 0,240                                   | 0,0410                                        |

| GaAs                   | 0,1                          | 3 500                          | 0,086                                      | 0,040                                   | 0,0069                                        |

\* La permittivité de stratifié verre/époxy a été fixée à 4,7.

Le point auquel une carte imprimée affecte de façon significative les caractéristiques de transmission d'une impulsion de propagation, largement cité dans le milieu des circuits imprimés, établit la comparaison entre le temps de montée et la longueur du trajet. Le principe consiste à déterminer, pour la transmission d'une impulsion à un temps de montée donné, la longueur d'un conducteur avant qu'une différence de tension importante ne se produise sur sa longueur. Les conducteurs dépassant cette longueur critique sont considérés comme des lignes de transmission. Si la chute de tension maximale est supérieure à la moitié de la valeur de la hauteur d'impulsion, le circuit est considéré comme une ligne de transmission. Cette longueur est importante en raison des autres considérations pratiques.

Pour des longueurs de trajet plus importantes, il n'est pas exclu que les réflexions provenant d'une impédance de charge mal adaptée soient reçues en retour à la source après que l'impulsion a atteint sa valeur à plateau maximal, et les additions d'impulsions survenant dans ces circonstances sont susceptibles de provoquer le déclenchement intempestif d'un dispositif. Pour des longueurs de trajet plus réduites, les impulsions réfléchies sont reçues en retour à la source avant que l'impulsion ait atteint sa valeur de plateau. Par conséquent, toute modification de la forme de l'impulsion se localisera au niveau du front de l'impulsion qui est moins susceptible de produire un déclenchement intempestif du dispositif. Les valeurs sont répertoriées dans la dernière colonne du tableau 2. On a suggéré de considérer les conducteurs de circuit dépassant 60 % de la longueur indiquée dans la dernière colonne du tableau 2 comme des lignes de transmission permettant une marge plus importante au niveau de la conception.

### 3.4.7 Temps de propagation

Dans les systèmes rapides, il n'est pas rare que le temps du cycle d'horloge soit plus court que le temps de propagation d'un signal d'un dispositif à l'autre. Pour que le système fonctionne correctement à vitesse élevée, un temps de propagation contrôlé est susceptible d'être nécessaire. Dans certains cas, des réglages du temps de propagation pour certains réseaux sont susceptibles d'être nécessaires en contrôlant la longueur totale d'attaque de la source à la charge.

#### 3.4.7.1 Temps de retard de propagation

La vitesse de propagation d'une onde électromagnétique est liée à la permittivité du moyen d'isolation selon la relation

$$V_p = \sqrt{\epsilon_r^{-0,5}}$$

frequency or the time domain. However, the critical point to remember for digital signals is that it is the pulse rise time, and not the rate at which the device is clocked, that is the key determining factor. The clock rate is a dependent parameter since the faster the rise time the faster a device can be clocked.

**Table 2 – Typical data for some logic families**

| Logic family | Rise time<br>ns | Bandwidth<br>MHz | Wavelength in free space |                                  |                                           |

|--------------|-----------------|------------------|--------------------------|----------------------------------|-------------------------------------------|

|              |                 |                  | In free space<br>m       | Epoxide/glass<br>laminat e*<br>m | 1/2 rise epoxide/<br>glass laminate*<br>m |

| TTL          | 8,0             | 44               | 6,800                    | 3,100                            | 0,5500                                    |

| Schottky TTL | 3,0             | 120              | 2,500                    | 1,200                            | 0,2100                                    |

| ECL          | 0,6             | 580              | 0,520                    | 0,240                            | 0,0410                                    |

| GaAs         | 0,1             | 3 500            | 0,086                    | 0,040                            | 0,0069                                    |

\* Relative permittivity of epoxide/glass laminate was taken as 4,7.